공머씨의 블로그

내가 공부한 논리회로 설계 21.XOR,XNOR게이트_Propagation delay.etc... 본문

내가 공부한 논리회로 설계 21.XOR,XNOR게이트_Propagation delay.etc...

공머씨 2020. 5. 31. 22:16저번 포스트에 있는 마지막 문제에 대한 풀이를 하고 XOR, XNOR게이트에 대한 설명을 하겠습니다.

풀이

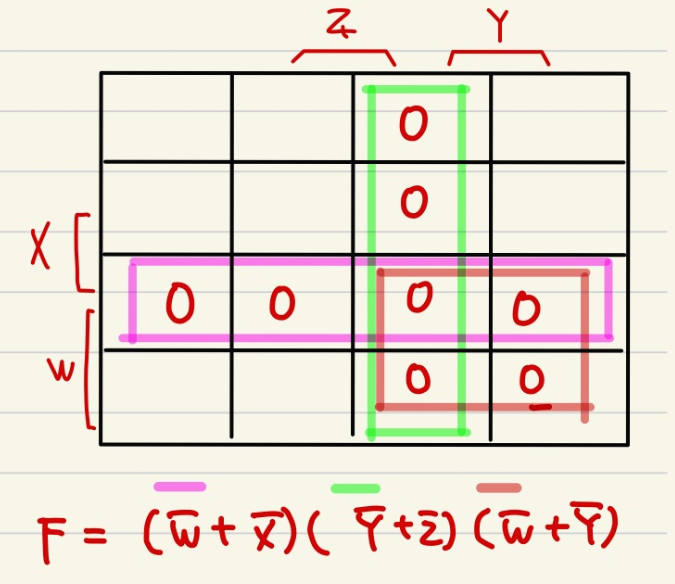

논리함수는 Maxterm형태로 주어졌습니다. 카르노 맵을 그리면 다음과 같습니다.

K-MAP을 이용해서 논리함수를 POS형태로 최적화하는 데에는 두 가지 방법이 있습니다.

1. /F의K-MAP을 작성하고 SOP로 최적화한 뒤 보수를 취해 POS형태를 구하는 방법

2. 주어진 Maxterm의 자리에 0을 대입하고 바로POS로 최적화하는 방법

1의 방법으로 K-MAP을 작성해서 논리함수를 POS형태로 얻으면 다음과 같습니다.

2의 방법으로 K-MAP을 작성해서 논리함수를 POS형태로 얻으면 다음과 같습니다.

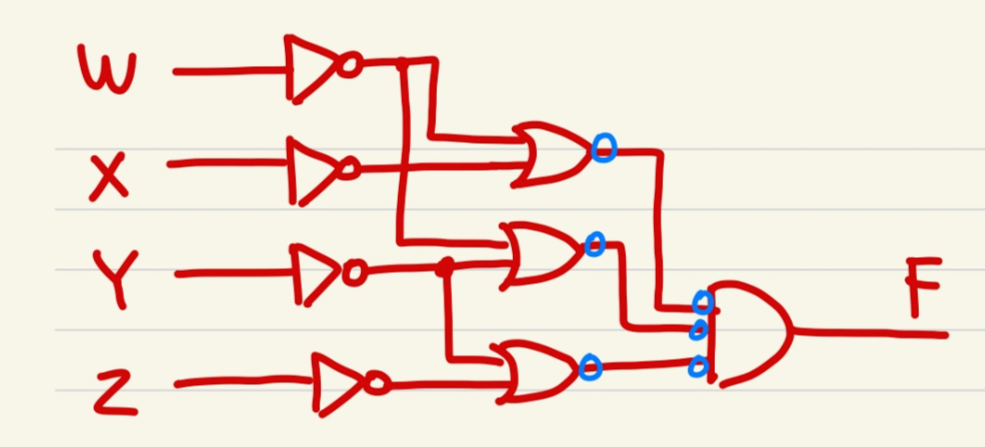

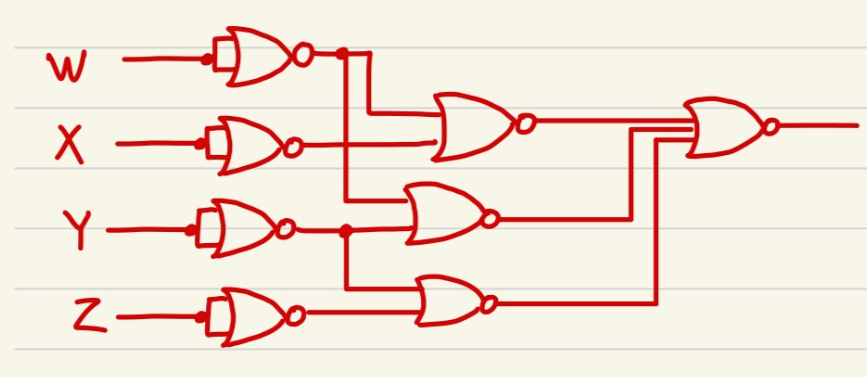

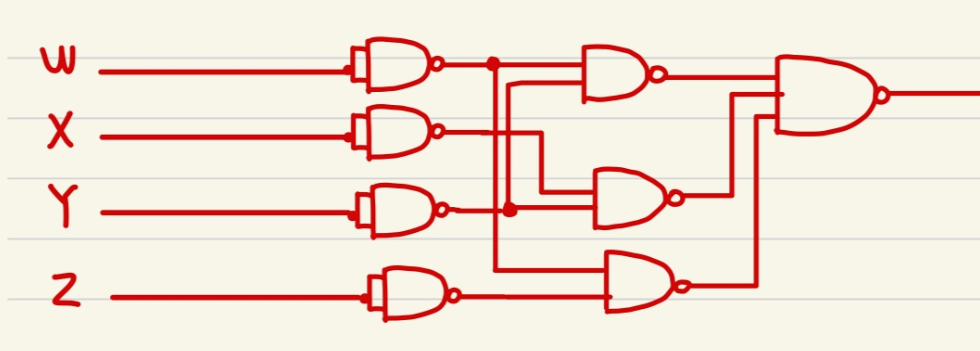

구한 논리함수로 일단 회로를 구현하면 다음과 같습니다.

NOT OR AND를 각각 NAND게이트로 바꾸면 됩니다.

SOP로 최적화하려면 1의 위치를 알면됩니다.

Maxterm으로 표기된 논리 함수가 0의 위치를 나타내므로 Maxterm이 존재하지 않는 위치가 1의 위치입니다.

XOR_GATE

XOR는 Exclusive OR의 약자입니다.

XOR는 어떤 소자이냐면

1) 입력에서 1의 개수가 홀수면 1을 출력하고 , 1의개수가 짝수이면 0을 출력합니다.

2) 입력의 갯수가 2개인 경우 입력의 값이 서로 다르면 1을 출력, 서로 같으면 0을 출력합니다.

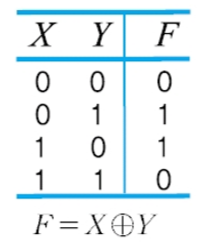

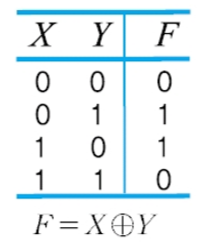

진리표를 봅니다.

F가 비워져 있다고 생각하고 봅니다.

첫 줄에서 입력에 1의 개수가 0개입니다. 짝수니까>>F=0

두 번째 줄에서 입력에1의 개수가 1개입니다. 1의개수가 홀수개이니까 >>F=1

....

이런 식으로 진리표를 채웁니다.

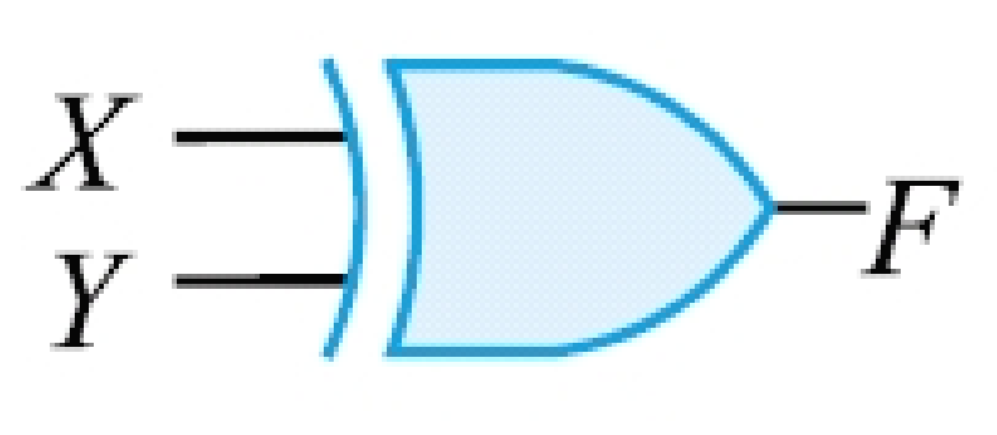

심벌은 다음과 같습니다.

OR게이트 앞쪽에 입력에 가까운 쪽에 짝대기를 하나 더 그리면 됩니다.

수식으로는 다음과 같이 작성합니다.

F=X⨁Y

F를 Sum of Minterms로 작성할 수도 있습니다.

진리표에서 출력이 1인 부분의 입력을 작성하면 (>>SOP형태로 작성하면 됩니다.)

/XY+X/Y

논리식으로 다음과 같이 작성합니다.

입력이 3개인 경우의 XOR게이트에 대해서 알아보겠습니다.

심벌로는 다음과 같이 나타냅니다.

진리표를 살펴보면 다음과 같습니다.

1의 개수가 홀수 개면 1, 짝수 개면 0을 출력합니다.

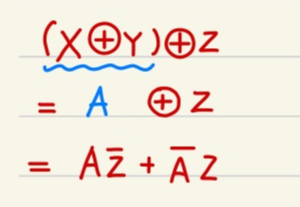

논리식으로 나타내면 다음과 같습니다.

X와 Y의 Exclusive OR를 A로 치환해보겠습니다.

치환한 뒤 지금까지 공부한 개념들을 이용해 전개해주면 됩니다.

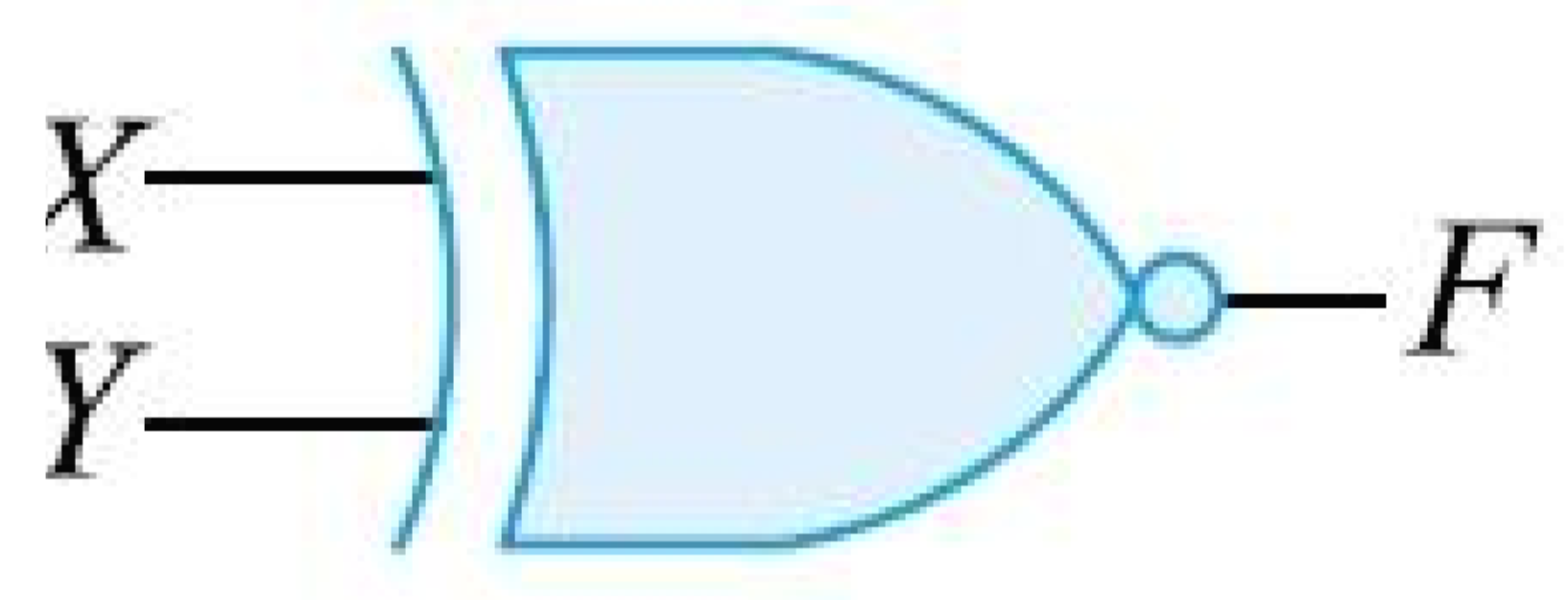

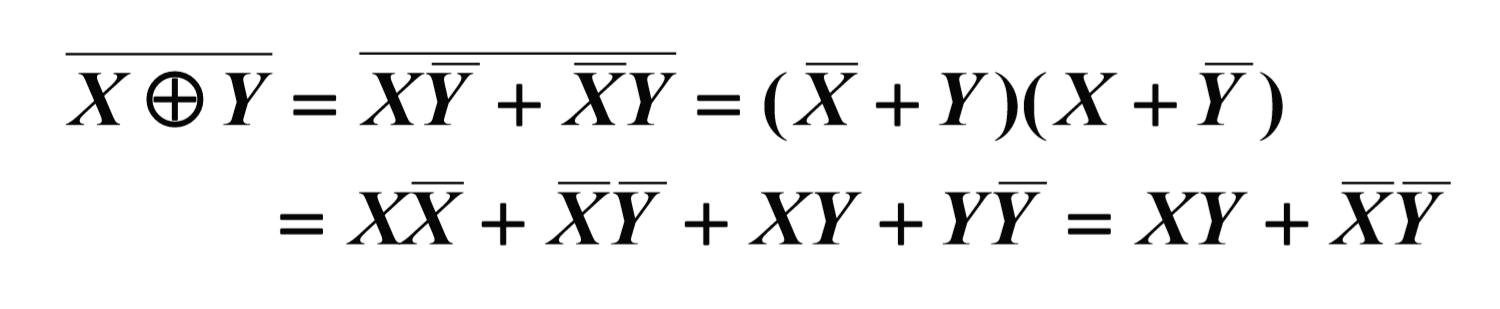

XNOR에 대해 알아봅니다.

Exclusive-NOR

XOR의 NOT입니다.

방금 공부한 XOR의 반대 특성을 갖게 됩니다.

심볼은 다음과 같습니다.

논리 함수는 다음과 같이 작성할 수 있게 됩니다.

F=/(X ⨁ Y)

진리 값이 XOR의 반대가 됩니다.

>> 반대 특성을 갖게 됩니다.

입력에서 1의 개수가 짝수일때 1을 출력하고 입력에서 1의개수가 홀수이면 0을 출력합니다.

(4글자니까 1이 짝수개일때 1을 출력)

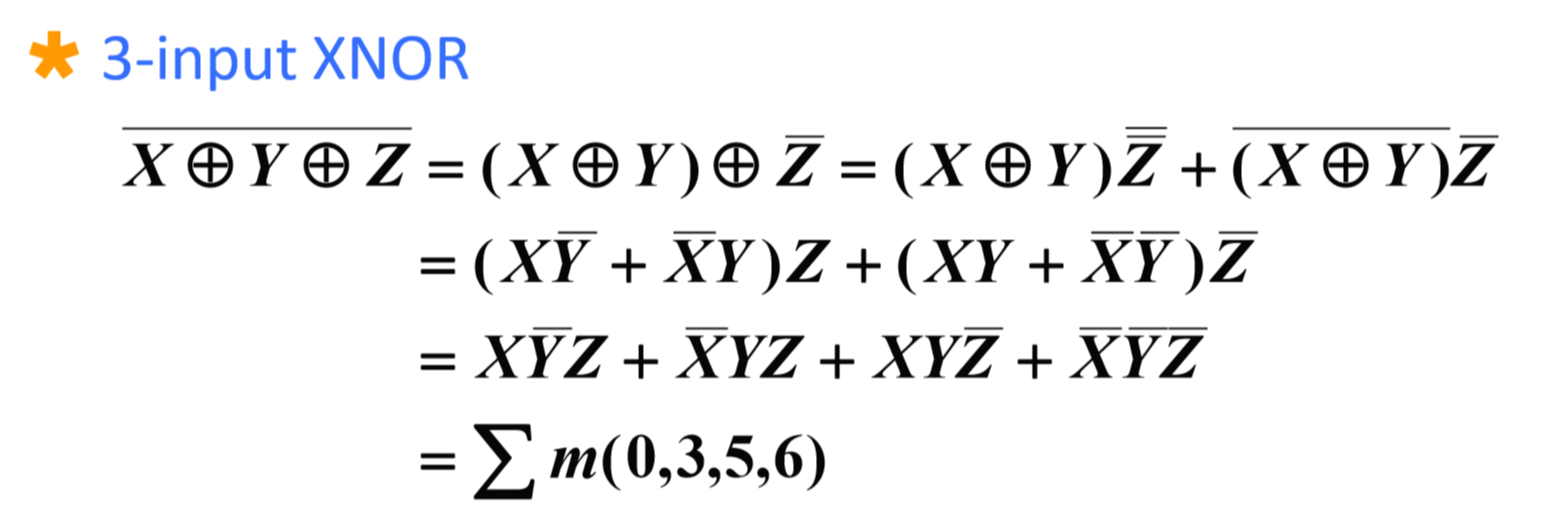

다음과 같은 진리표를 가집니다.

F는 /(X⨁Y)

전개해보면 다음과 같습니다.

입력이 3개인 경우도 똑같이 계산할 수 있습니다.

그 다음 중요한 내용이 있습니다.

일단 다음과 같은 진리표를 기억하고 있어야 합니다.

F부분을 가리고 직접 그려보길 바랍니다.

XOR와 XNOR의 기본적이고 중요한 특징을 알아보겠습니다.

1.X에 0을 Exclusive OR 하면 무엇이 되는가?

X에 값을 대입해보면 왜 그런지 알 수 있습니다.

0을 대입하면 0과 0의 Exclusive OR이기 때문에 0 이 나옵니다.

반대로 1을 대입하면 1이 나옵니다.

대입하는 숫자가 그대로 나오므로

다음과 같이 작성하면 됩니다.(전개해보면 됨)

2. X와 1의 XOR는?

X가 0인 경우, X가 1인 경우를 각각 대입해보면 됩니다.

3.X와 X의 XOR는?

항상 0 임을 알 수 있습니다.

4.X와/X의 XOR는?

입력이 무엇이든지 상관없이 결과가 항상 1 임을 알 수 있습니다.

참고해서 보면 됩니다.

XOR XNOR게이트를 어디에 활용할 수 있는지를 알아봅니다.

>>Parity, EvenParity를 만드는 데 사용할 수 있습니다.

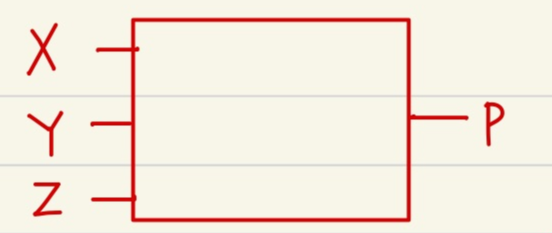

3비트가 있는데 마지막에 Even parity CODE를 넣고 싶다면

마지막 칸에 1을 넣으면 됩니다.

회로로 만들기 위해서는 XOR게이트가 하나 있으면 쉽게 만들 수 있습니다.

(XOR: 1이 홀수개이면 1을 출력한다.)

입력이 3Bit에다가 출력이 p인 함수를 만들고 싶다면 전체 1의 개수가 짝수가 되어야 합니다.

3Bit일 때 입력의 모든 경우의 수에 대한 ParityBit의 진리표는 다음과 같습니다.

Parity Bit에

입력의 1의 개수가 짝수개이면 0을 넣으면 되고

홀수 개면 1을 넣으면 됩니다.

입력에 1의 개수가 짝수면 0,입력에 1의 개수가 홀수면 1을 만드는 소자가 XOR소자였습니다.

XOR게이트와 EvenParity가 하는 일이 같습니다.

최종적으로 다음과 같은 회로를 그릴 수 있습니다.

그 다음 수신기에서 XYZP를 입력받은뒤,

EvenParity Chcheker 수신부에서 오류가 있는지 없는지 판단하려고 한다면,4 input XOR게이트를 사용하면 됩니다.

Q값이 0이면 1의 개수가 짝수개 no error, (Even Parity를 만드는 과정이니까)

Q값이 1이면 XOR의 출력이 1이라는 것이므로 입력의 1의 개수가 홀수라는 이야기입니다. Error이 있다고 판단합니다.

이런식으로 EvenParity의 생성과 검산은 XOR게이트로 할 수 있습니다.

OddParity비트의ㅡ 검산은 XNOR게이트로 할 수 있습니다.

원리와 과정은 위와 같습니다.

(XNOR:입력의1의개수가 짝수개이면 1을 출력)

HighHigh-Impedance Outputs는 넘어갑니다. (2학기-"디지털 시스템 설계"과목에서 공부합니다.)

3-STATE BUFFER을 이용해서 메모리 (SRAM, DRAM의 구조를 이해하기 위해 필요하다. )

나중에 공부하도록 합니다.

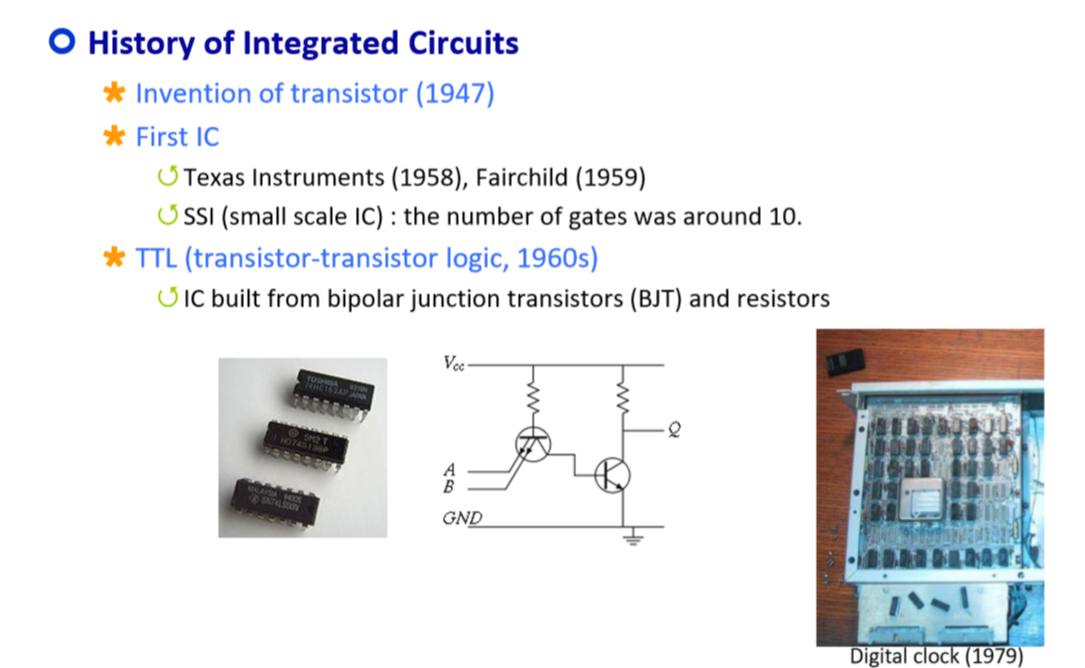

마지막으로 Characteristics of Logic Gates 논리소자들의 개발에 대한 이야기입니다.

트랜지스터는 1947년 TI라는 회사에서 만들었다고 합니다.

집적회로는 1958년 만들었다

1950년대만 해도, SSIC밖에 없었습니다.

게이트가 10개 정도 집적되어있는 칩입니다.

TTL이라고 하는 칩들이 개발 실험실에서 구현할 때 사용하게 될 것이다.

40년 전쯤에 디지털시계를 만들었습니다.

발진기 Osclilate 부품도 있는 것을 볼 수 있습니다. couting 하는 역할을 하는 부품입니다.

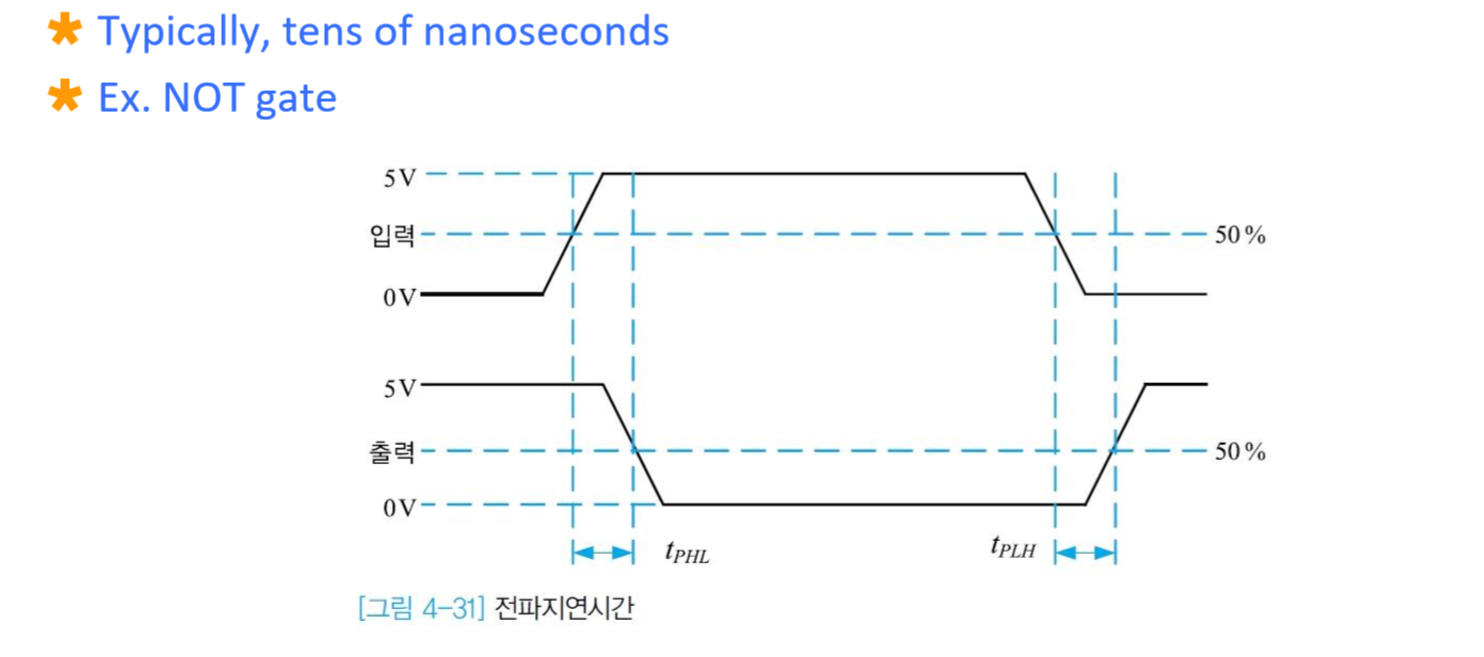

PROPAGATION DELAY- 전송 지연

NOT게이트가 하나 있다고 생각해봅니다.

입력은 X고 출력은 F

위쪽은 X의 파형을 그린 것입니다.

출력은 대칭이 됩니다...?라고 생각하겠지만, 사실은 전혀 그렇지 않습니다.

직각형태는 존재할 수 없다고 합니다.위의 그림보다 더 부드러운 모양입니다. (이는 나중에 더 깊게 공부합니다.)

또한, 입력이 위의 신호와 같이 들어온다고 해도 바로 대칭으로 출력되는 것이 아닙니다.

입력과 출력은 약간의 시간 차이가 있다고 합니다. (소자를 거쳐서 나오기 때문에 시간이 걸립니다.)

PROPAGATION DELAY는 두 종류가 있는데

High에서 low로 가는 Delay와

low에서 High로 가는 Delay가 있습니다.

화살표만큼의 시간을 High에서 Low로 가는 Delay라고 합니다.

tPHL이라고 표현을 합니다.

반대로 NOT게이트의

low에서 High로가는 Delay가 존재합니다.

거의 같거나 유사합니다.

이렇게 간단한 회로에서 나타나는 전송 지연시간은 1 nano second 정도 된다고 합니다.

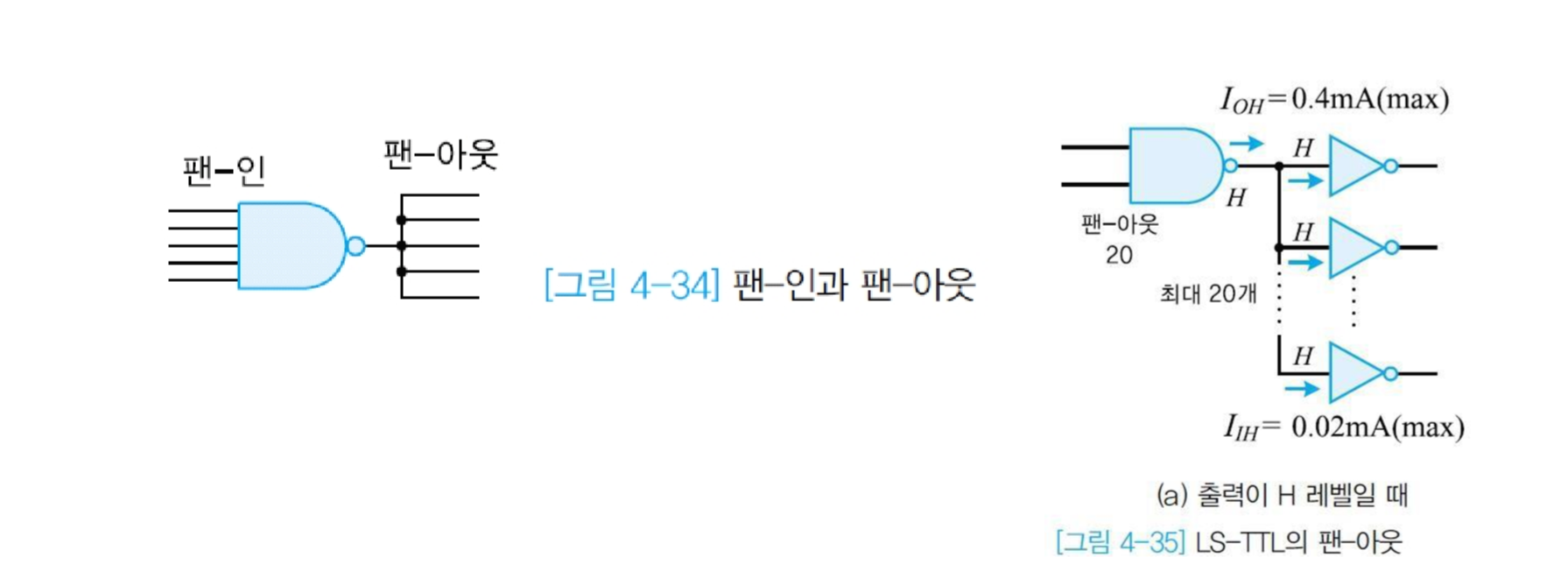

FAN -in FAN-out을 알아봅니다.

FAN -in은 최대로 허용 가능한 입력의 개수입니다.위 소자에서는 5개입니다.

FAN-out은 최대로 허용 가능한 출력의 개수입니다위 소자에서는 5개입니다.

소자의 FAN -in, FAN-out개수를 알려면 각소자에 대한 Data Sheet를 봐야 합니다.

NAND게이트에서 출력의 전류가 400mA라고 하면

출력에 NOT게이트를 20개로 늘렸다고 가정합니다.

키프히호프 전류 법칙에 의해 400mA를 20개의 소자로 균등하게 공급하면 한 소자당 20mA를 공급하게 됩니다.

위의 내용이 어렵다면, " FAN -in은 입력에 붙을 수 있는 최대 가짓수, FAN-out은 출력에 붙을 수 있는 최대 가짓수"

정도로만 알아두면 됩니다.

지금까지 조합 회로를 해석하는방법에 대해 공부했습니다.

이제 다음 단원부터는 조합회로를 설계하는 방법을 공부합니다.

도움이 되셨다면 로그인이 필요없는 하트버튼 한번 부탁드립니다!!

'내가 공부한 3학기 전공 > 내가 공부한 논리회로 설계' 카테고리의 다른 글

| 내가 공부한 논리회로 설계 23.(13-1_Code converter,7 segment LED) (0) | 2020.06.11 |

|---|---|

| 내가 공부한 논리회로 설계 22. Combinational circuit Design(Mathodology_Examples)_Majority v (0) | 2020.06.11 |

| 내가 공부한 논리회로설계 20.Other Gates (NOR,NAND) (0) | 2020.05.28 |

| 내가 공부한 논리회로 설계 19. POS_Don't Care (0) | 2020.05.19 |

| 내가 공부한 논리회로 설계18. PI, EPI (0) | 2020.05.19 |