공머씨의 블로그

내가 공부한 논리회로 설계 26(14-2)_Multiplexer 본문

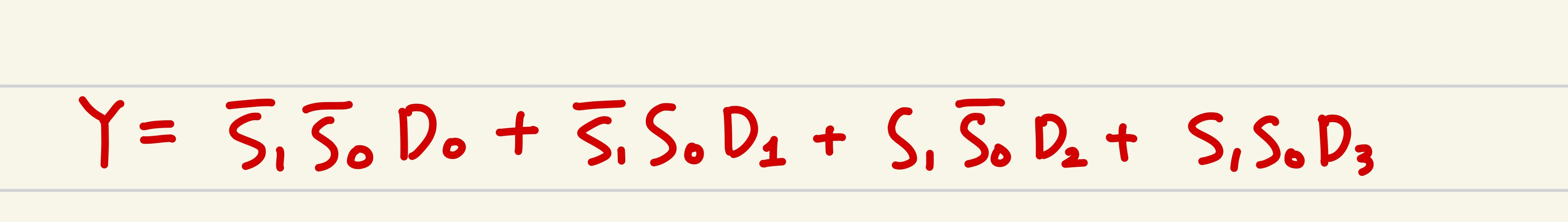

4⨉1 MUX

데이터 입력이 4개이고 출력이1개인 4⨉1 MUX를 공부해보겠습니다.

어떤경우(S값에 따라) D0를Y에 연결,어떤 경우에 D1을 Y에 연결,,,, 이런게 MUX였습니다.

Selection이 2Bit가 더 필요하다. (입력이 4가지 경우의 수가 있기때문에)

S1과 S0가 0,0이라면 출력Y는 D0가 됩니다.

S1과 S0가 0,1이라면 D1이 Y에 연결되도록 합니다.

S1과 S0가 1,0이라면 D2가 출력에 연결되도록 합니다.

모두 1이라면 D3가 연결되면 되겠다. 라고 생각하면됩니다.

이 회로를 만들어야 되는데 출력Y를 입력의 함수로 작성해야되는데

... 아까처럼 두가지 방법을 생각한다면

1. 진리표작성,K-MAP작성

2.IF ELSE문이용

1번의 방법으로는 굉장히 어렵습니다. 입력이 6개이기 때문에 많은 출력이 필요하게 됩니다.

Table을 보고 S1=0 S2=0일때부터 1,1이 될때까지 하나씩 대입해보면 논리함수등식이 성립함을 알 수 있습니다.

회로를 구현하면 다음과 같습니다.

2⨉1 MUX인데,EN이 있는 경우입니다.

EN이 0일경우S에 관계없이 출력이 항상 0 이 됩니다.

Enable이 1일때는, 2⨉1 MUX처럼 동작합니다.

EN이 1일때 S가 0이면 출력은D0

EN이 1일때 S가 1이면 출력은D1이되는 회로 입니다.

논리함수Y를 작성해봅니다.

회로를 구현 하면 다음과 같습니다.

4-bit 2⨉1 MUX를 도식화화면

A가 4bit, B도 4bit 입니다.

S에 따라 A 4BIT가 출력되거나, 입력B의 4BIT가 출력되게 됩니다.

지금까지공부한 MUX회로는 다음그림과 같았다면

4-bit 2⨉1 MUX는 다음과 같습니다.

여기까지MUX를 구현해보았습니다.

MUX를 여러가지 방법으로 구현할수 있습니다.

DE MUX는 MUX와 반대기능을해서 MUX의 입력과 출력이 뒤바뀌어 있는 형태입니다.

18~21페이지 생략

조합회로를 구현하는데 조합회로를 LD를 가지고 MUX를 가지고도 만들수 있습니다.

LD와 MUX를 활용해서 조합회로를 만드는것을 공부해봅니다.

LD를 이용해서 조합회로를 만드는것은 매우 쉽습니다.

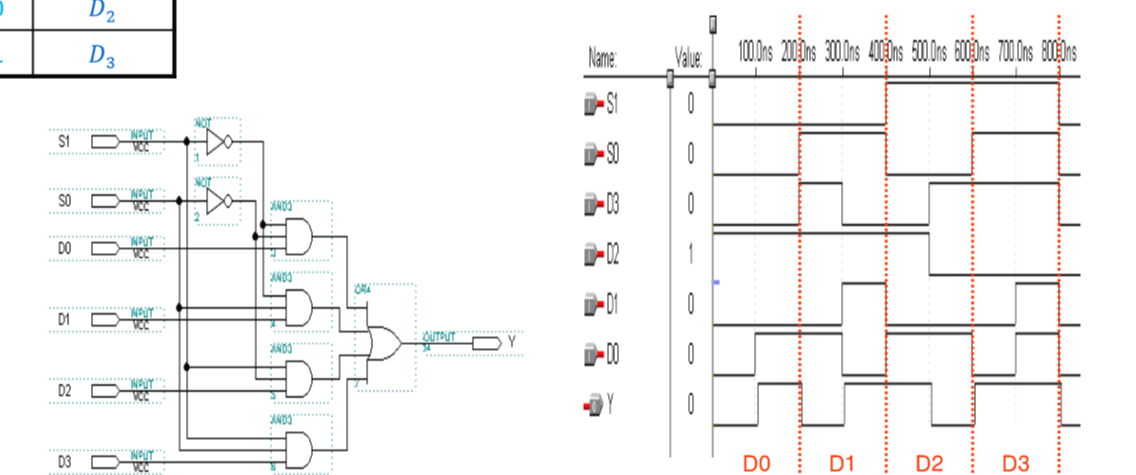

입력은 X Y Z이고 출력은C S입니다.

8가지 기능을 수행하는,진리표대로 동작하는 회로를 만듭니다.

진리표를 보고,K-MAP으로 표현한뒤 회로를 구현했습니다.

그렇게 안하고 LD를 가지고 구현해봅니다.

출력C,S에 대한 K-MAP를 그려서 X Y Z의 함수로 표현해서 AND OR게이트로 구현했었는데 그렇게 안하고

LD를 가지고 구현을 해봅니다.

출력이 입력의 Minterms으로 구성되어있다고 공부했습니다.

A2에 X라는 입력을 ,A1에 Y, A0에 Z라는 입력을 맵핑시킵니다.

D들의 출력은 위와 같습니다.

LD를 사용해서 조합회로를 만들수도 있는데 기본적으로 LD의 출력은 입력의 Minterms이기 때문에

Sum of minterm으로 표현하면 회로를 구현할 수 있습니다.

진리표와 회로가 완전히 같게됩니다.

여기서 중요한 사실은 입력의 순서맵핑입니다.

순서가 뒤바뀌면 ..........

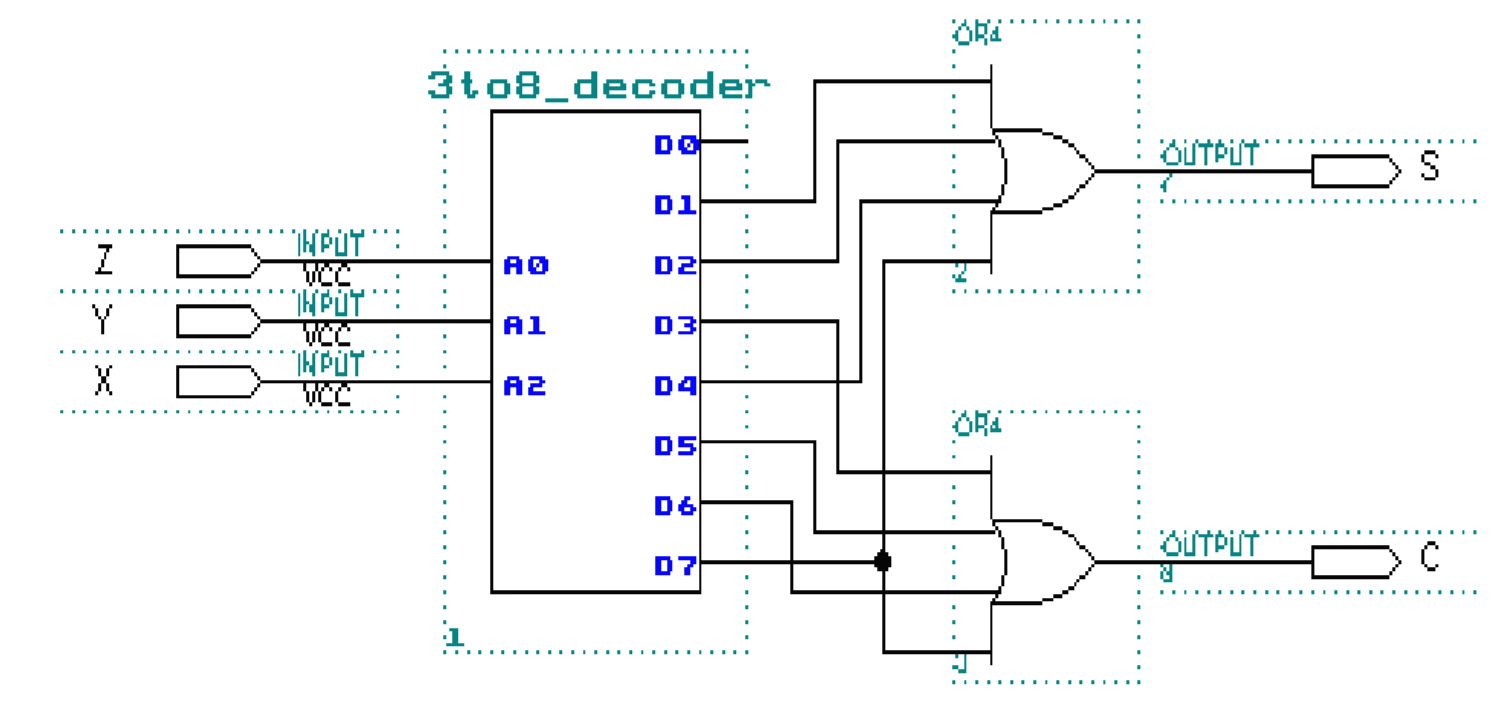

다음은 MUX를 사용해서 조합회로를 만들 수도 있습니다.

다음과 같은 회로를 MUX를 이용해서 만들려고하는데

MUX S1 S0가 0 0 이면 출력 D0가 Y인 것입니다.

잘 활용하면 이회로를 MUX에 구현할 수 있게됩니다.

첫번째 변수 X랑 두번째 입력변수 Y를 S1 과 S0에 각각 맵핑시킵니다.

X가 0이고Y가 0일때

Z가 0이면 출력F=0

Z가 1이면 출력은 1이라는것을 알 수 있습니다.

즉, X,Y가 00 일때 F는 Z의 입력과 같습니다.

D0가 Y에 출력될 것 입니다.

D0에 Z를 연결하면 됩니다. (출력Y는 Z가 나옵니다.) 왜 X Y 00일때 D0인거지?

두가지 기능을 수행할 수 있게 됩니다.

이해가 안되었다면 두번째 줄을 보겠습니다.

S1이 0이고 S0가 1

X가0 Y가1일때

Z가0이면 출력은 1, Z가 1이면 출력은 1

다시 말해서 X가0 Y가1일때,출력은 /Z이라고 생각하면 됩니다.

X가 1이고 Y가 1이라면 Z값에 상관없이 모두 1이 나와야 합니다.

입력을 1로 넣으면 됩니다.

진리표와 동일한 기능을 하는 회로를 만든것이 됩니다.

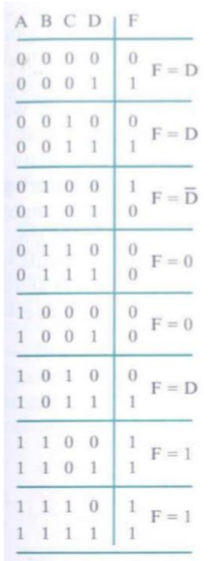

이번에는 입력이 4개인 다음과 같은 회로를 알아보겠습니다.

다음과 같은 진리표와 8⨉1 MUX가 주어져 있습니다.

진리표를 보고 회로를 어떻게 설계할지 판단하면 됩니다.

지금까지 조합회로를 설계하는 방법을 공부해보았습니다.

'내가 공부한 3학기 전공 > 내가 공부한 논리회로 설계' 카테고리의 다른 글

| 내가 공부한 논리회로 설계 27(14-3) _Binary Adder (2) | 2020.06.16 |

|---|---|

| 내가 공부한 논리회로 설계 25(14-1)_Mutiplexer (2) | 2020.06.15 |

| 내가 공부한 논리회로 설계 24.(13_2.Coder_Line Decoder_Encoder) (0) | 2020.06.11 |

| 내가 공부한 논리회로 설계 23.(13-1_Code converter,7 segment LED) (0) | 2020.06.11 |

| 내가 공부한 논리회로 설계 22. Combinational circuit Design(Mathodology_Examples)_Majority voting circuits (0) | 2020.06.11 |